2D FFT

Fast and efficient two-dimensional FFT core for image processing applications.

Successful FPGA/ASIC implementation of two-dimensional FFTs (used in 2D image processing applications) requires deep understanding of the underlying 1D FFT algorithm, chip and memory architectures. Since each pixel of image data is effectively processed twice, the issues of throughput, scaling, resource usage, and memory interfacing all become intertwined when considering the optimal solution for the target chip architecture.

Successful FPGA/ASIC implementation of two-dimensional FFTs (used in 2D image processing applications) requires deep understanding of the underlying 1D FFT algorithm, chip and memory architectures. Since each pixel of image data is effectively processed twice, the issues of throughput, scaling, resource usage, and memory interfacing all become intertwined when considering the optimal solution for the target chip architecture.

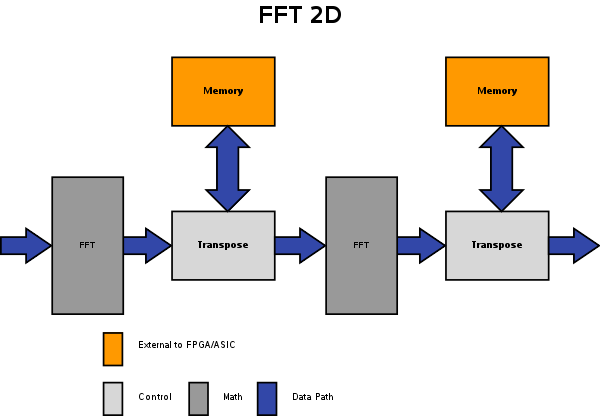

Block Diagram

Block diagram with external memory used for storage during the two required data transposes.

Versatile IP

At Dillon Engineering, we have provided our customers with efficient 2D FFT solutions, taking into consideration a number of design trade-offs, including:

- FFT IP engines with variable lengths and robust scaling options

- Continuous processing

- Resource sharing

- Transpose memory implemented on- or off-chip

- External SRAM or DRAM with on-chip caching where required

Performance

The performance of a 2D FFT is limited by the bandwidth of the transpose memory. Each 2D FFT IP Core delivered by Dillon Engineering is configured to obtain maximum performance based upon the internal or external memory architecture available.

More Information

For details on 2D FFT algorithm processing, see our FFT Success article on the subject. Count on the experts at Dillon Engineering for fast and efficient implementation for all your image processing applications.

Device Fit Estimate of Additional Information

Fill out the FFT IP Fit/Information Form to obtain a device usage estimate in your target technology or to obtain additional information about a specific FFT architecture.