Parallel FFT

Full parallel FFT IP, the fastest and most efficient FFT architecture for short FFTs

Key Features

Key features of the fully parallel FFT IP Core

- Fastest most power efficient architecture optimized for short FFTs, 4 to 64 points

- Optimized Butterflies/Dragonflies, reductions from constant twiddle factors reduces logic

- No pipeline limit, fully asynchronous to maximum pipeline stages

- N points in/out per clock cycle, ultra high performance, 25 GSPS+ possible in FPGA

- lengths up to 64 points practical in FPGAs

Performance

Performance example for the Parallel FFT IP Core with the following features:

- Virtex-5

- 400 MHz clock

- 32 bit complex I/O (16 real/imag)

- Speed is in GSPS (giga samples per second)

| Length |

Speed (GSPS) |

Slices |

bRAMs |

DSP48s |

|---|---|---|---|---|

| 16 |

6.4 |

1,283 |

0 |

20 |

| 32 |

12.8 |

5,068 |

0 |

80 |

| 64 |

25.6 |

9,875 |

0 |

208 |

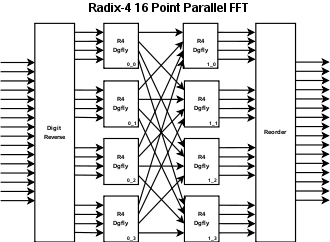

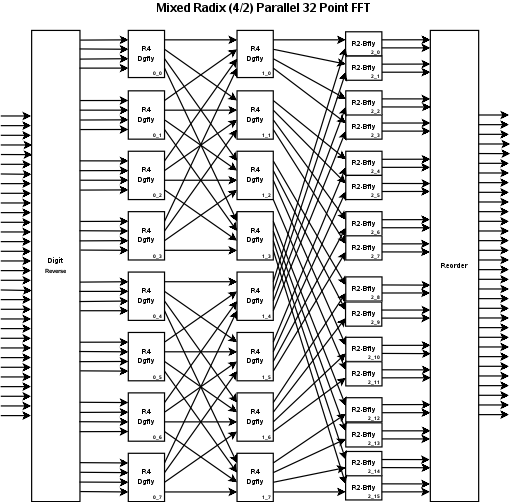

Block Diagrams

Two fully parallel FFT IP are shown, a radix-4 16 point FFT and a mixed radix-4/2 32 point. Just two examples of the fully parallel IP available.

Device Fit

Estimate or Additional InformationFill out the FFT IP Fit/Information Form to obtain a device usage estimate in your target technology or to obtain additional information about a specific FFT architecture.