Mixed Radix FFT

FFT using any combination of radix-2, -3, -5, or -7 factors

Real-world processing such as LTE OFDM often require non power-of-2 or -4 FFT lengths for spacing into the desired frequency bin size, called mixed-radix FFTs.

At Dillon Engineering, we have helped our customers achieve optimal mixed-radix FFT solutions, with design considerations such as:

At Dillon Engineering, we have helped our customers achieve optimal mixed-radix FFT solutions, with design considerations such as:

- Any combination of radix-2, -3, -5, and -7 factors.

- Combination parallel and serial FFT engines

- Continuous data processing

- Latency constraints

- Internal or external memory budget

Key Features

Key features of the mixed radix FFT IP Core.

- Lengths other than radix-2 possible (i.e. 768, 256 x 3)

- Parallel FFT structures to increase performance

- Fixed or floating point math

- Wide range of performance options

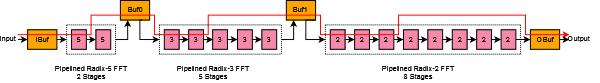

Block Diagram

Block diagram of a pipelined Mixed Radix-2/3/5 FFT, an example of one of the many Mixed Radix FFT architectures Dillon Engineering has available. In this single-stream pipelined structure, the superset supports a length of 52 * 35 * 28 = 1,555,200 points. The red dataflow line shows pipelined processing order of 360 points (51 * 32 * 23).

For an example of a parallel 768-point FFT, see the Xilinx architecture-specific link below.

Architecture Specific Options

Additional Information

For more information, see our HPEC 2003 Presentation on mixed-radix FFT processing.

Device Fit Estimate or Additional Information

For more information, see our HPEC 2003 Presentation on mixed-radix FFT processing.

Fill out the Mixed Radix FFT IP Fit/Information Form to obtain a device usage estimate in your target technology or to obtain additional information about a specific FFT architecture.

Fill out the Mixed Radix FFT IP Fit/Information Form to obtain a device usage estimate in your target technology or to obtain additional information about a specific FFT architecture.