FFT_PIPE IP Core for Xilinx FPGAs

True Floating Point Pipelined FFT processing for Xilinx FPGAs

Description

Dillon Engineering's Pipelined Floating Point FFT IP Core uses a modular radix-2 Fast Fourier Transform (FFT) architecture to provide discrete transforms on data frames or continuous data streams, with sample rate up to the maximum clock frequency. This efficient structure employs a single butterfly and a single delay feedback path per rank for low localized memory usage. True IEEE-754 floating point data maintained throughout, supporting a large dynamic range of data without requiring complicated fixed-point analysis. The Pipelined IP Core is easily scalable to any Xilinx device and customizable to suit many FFT applications.

Features

- Radix-2 Fast Fourier Transform (FFT) with pipelined butterfly rank structure

- IEEE-754 Floating Point data

- Uses Xilinx Coregen math operators

- Customizable precision, speed, and size

- Any width fixed-point builds also available

- Run-time selectable length N=32 to 2m, (m=5-16)

- See table below for example 2m max length builds

- Length up to N=64K (m=16) possible in Virtex-5 SX240

- Run-time selectable Forward/Inverse transform mode

- Continuous processing at speeds up to Fmax (see table).

- Data rate of 250MSamples/sec in Virtex-5.

- Natural-order inputs and outputs

- Includes C/C++ bit-accurate model and data generator

- Model also usable from MATLAB

- Includes Verilog testbench and run scripts

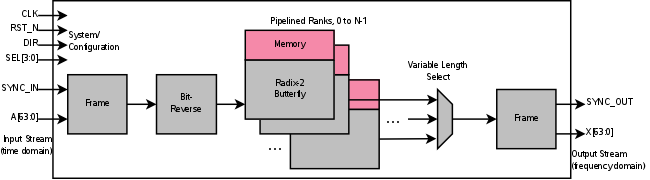

Block Diagram

FFT_PIPE IP block diagram:

Xilinx FPGA Resource Usage

Example Implementation Statistics for Xilinx FPGAs

|

Family |

Device |

Length |

FMAX |

Slice FF1 |

Slice LUT1 |

IOB2 |

GCLK |

BRAM |

MULT DSP48 |

|---|---|---|---|---|---|---|---|---|---|

|

Spartan®-3A |

XC3SD3400A-5 |

256 |

150 |

34,299 |

32,100 |

137 |

1 |

16 |

96 |

|

Virtex®-4 |

XC4VSX55-12

|

1,024 |

200 |

38,370 |

28,547

|

137 |

1 |

24 |

352 |

|

Virtex®-5 |

XC5VSX50T-3 |

1,024 |

250 |

27,690 |

20,243 |

137 |

1 |

19 |

176 |

|

Virtex®-5 |

XC5VSX95T-2 |

16,384 |

200 |

39,810 |

29,439 |

137 |

1 |

109 |

256 |

Notes:

- Actual slice count dependent on percentage of unrelated logic – see Mapping Report File for details

- Assuming all core I/Os and clocks are routed off-chip.

Additional Information

For additional information view the FFT_PIPE Datasheet.

Fill out the FFT_PIPE IP Fit/Information Form to obtain a device usage estimate for another target technology or to obtain additional information about the FFT_PIPE IP Core.

Fill out the FFT_PIPE IP Fit/Information Form to obtain a device usage estimate for another target technology or to obtain additional information about the FFT_PIPE IP Core.